Flip-flop je izraz, ki spada pod digitalno elektroniko in je elektronska komponenta, ki se uporablja za shranjevanje ene same informacije.

Diagramska predstavitev japonke

- Ker je Flip Flop zaporedno vezje, njegov vhod temelji na dveh parametrih, eden je trenutni vhod, drugi pa izhod iz prejšnjega stanja.

- Ima dva izhoda, oba se dopolnjujeta.

- Lahko je v enem od dveh stabilnih stanj, 0 ali 1.

Osnovni diagram flip flopa

Kaj je T Flip Flop?

- T flip flop ali če smo natančni je znan kot Toggle Flip Flop, ker lahko preklaplja svoj izhod glede na vhod.

- T tukaj stoji za Preklopi .

- Preklop v bistvu pomeni, da bo bit obrnjen, tj. bodisi z 1 na 0 ali z 0 na 1.

- Tukaj je za delovanje tega flopa dobavljen taktni impulz, zato gre za taktni flip-flop.

Konstrukcija T Flip Flop

T flip lahko konstruiramo na tri načine, in sicer:

- Z uporabo japonk SR.

- Z uporabo D Flip Flops.

- Z uporabo JK Flip Flops

Načini konstruiranja T flip flopa

Oglejmo si konstrukcijo T Flip Flop z uporabo SR Flip Flops, ki zahteva 2 IN in 2 NOR vrata, kot je prikazano spodaj:

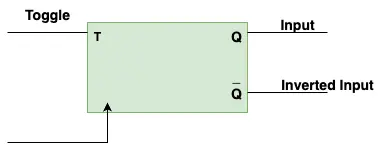

Osnovni blokovni diagram T flip flopa

Tukaj blokovni diagram vsebuje vhode za preklop in uro, Q in Q' pa sta dopolnjena vhoda.

Delovanje T Flip Flop

Primer 1 : Recimo, T = 0 in urni utrip je visoka tj. 1, potem bo izhod obeh IN vrat 1 IN vrat 2 0 , vrata 3 izhod bo Q in podobno vrata 4 izhod bo Q' tako sta obe vrednosti Q in Q’ enaki prejšnji vrednosti, kar pomeni Zadrži stanje .

Primer 2 : Recimo, T=1 , potem bo izhod obeh IN vrat 1 (T * ura * Q) , in ker sta oba T in ura 1, bo izhod vrat IN 1 enak Q , in podobno bo izhod vrat IN 2 (T * ura * Q’) tj. Q' . Zdaj bo izhod vrat 3 (Q'+Q)' in recimo, da je Q' nič, potem bo izhod vrat 3 enak (0+Q)' kar pomeni Q' in podobno bo izhod vrat 4 (Q+Q')' in ker je Q' nič, bo izhod vrat 4 Q', kar pomeni 0 ker je Q' nič. Zato lahko v tem primeru rečemo, da se izhod preklaplja, ker T=1 .

Tabela resnice T Flip Flop

- Tu je T preklopni vhod, Q je vhod trenutnega stanja, Qt+1 je naslednji izhod stanja.

- Od tu lahko vidimo, da je, kadar je Preklop (T) 0, naslednji izhod stanja (Qt+1) enak vhodu trenutnega stanja (Q).

- Kadarkoli je Preklop (T) 1, bo naslednji izhod stanja (Qt+1) dopolnilo vhodu trenutnega stanja (Q), kar pomeni, da se preklopi.

Karakteristična enačba

- Karakteristična enačba nam pove, kakšno bo naslednje stanje flip flopa glede na trenutno stanje.

- Da bi dobili značilno enačbo, se sestavi K-Map, ki bo prikazan spodaj:

- Če rešimo zgornjo K-karto, bo karakteristična enačba Q(n+1) = TQn’ + T’Qn = T XOR Qn

Tabela vzbujanja

Tabela vzbujanja v bistvu pove o vzbujanju, ki ga flip flop potrebuje za prehod iz trenutnega stanja v naslednje stanje.

- Tukaj, kadar je T 0, je Qt+1 enak vhodu Q.

- In kadar koli je T 1, je Qt+1 komplement vhoda Q.

Uporaba T Flip Flop

Obstajajo številne aplikacije T Flip Flop v digitalnem sistemu, ki so navedene spodaj:

- Števci : T Flip Flops, ki se uporabljajo v pultih. Števec šteje število dogodkov, ki se zgodijo v digitalnem sistemu.

- Shranjevanje podatkov : T Japonke, ki se uporabljajo za ustvarjanje pomnilnika, ki se uporablja za shranjevanje podatkov, ko je napajanje izklopljeno.

- Sinhronska logična vezja : T flip-flops se lahko uporabljajo za implementacijo sinhronih logičnih vezij, ki so vezja, ki izvajajo operacije na binarnih podatkih na podlagi signala ure. S sinhronizacijo operacij logičnega vezja s signalom ure z uporabo T flip-flopov je lahko vedenje vezja predvidljivo in zanesljivo.

- Frekvenčna delitev : Uporablja se za deljenje frekvence signala ure z 2. Flip-flop bo preklopil svoj izhod vsakič, ko signal ure preide iz visokega v nizek ali nizkega v visok, s čimer se frekvenca ure deli z 2.

- Shift registri : T flip-flops se lahko uporabljajo v preklopnih registrih, ki se uporabljajo za premik binarnih podatkov v eno smer.

Zaključek

V tem članku izhajamo iz osnov japonk, kaj pravzaprav so japonke, nato pa smo razpravljali o japonkah T, treh dveh načinih, na katere lahko sestavimo japonke T, to je osnovni blokovni diagram, delovanje japonk T , to je tabela resnic, karakteristična enačba in tabela vzbujanja, na koncu pa smo razpravljali o uporabi T japonk.